NASR-M board bring-up, USB adventures II

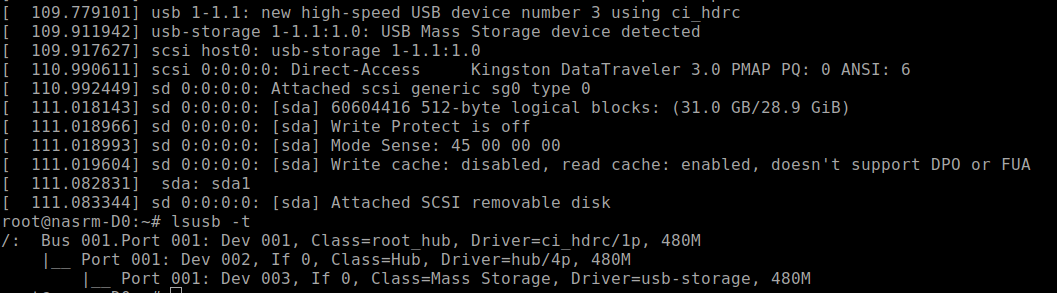

USB finally works. Now I’m able to connect an external USB hub to the socket and plug in thumb drives and USB hard disks. All works fine, except the USB-to-SATA converter, which is not soldered in yet. I saved that for the dessert, because I have other priorities.

This is the ‘lsusb -t’ picture of a thumb drive plugged into the USB socket.

NASR-M board bring-up, USB adventures

It’s USB show time! Xilinx documents suggest the USB3320 as a good USB PHY that works, and I’ve seen multiple development boards that use that chip. If it works for them, it will probably work for me, I thought. Despite being defined in Vivado hardware design, USB was not detected by the Linux kernel. Looking closely, I saw that a reference clock was ok, but there was no signal on the CLKOUT pin.

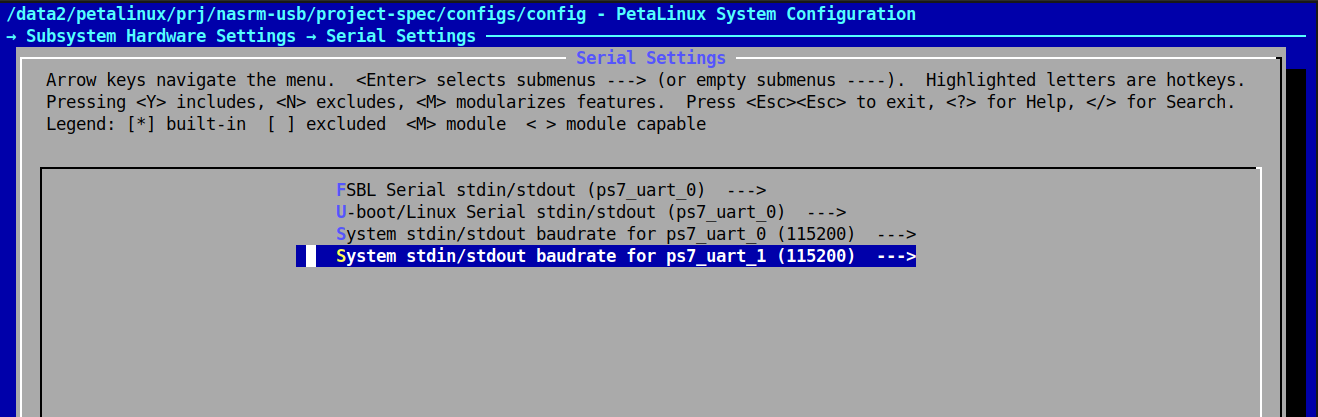

Petalinux Zynq configuration order

This is a short reminder to myself on how to configure the Petalinux for Zynq 7000.

First, source the settings.sh from the Petalinux root folder.

source ./settings.sh

Create the project from Vivado hardware definintion export. It's a good idea to provide a complete path to the xsa file.

petalinux-create project --template zynq --name nasrm-usb

cd nasrm-usb

petalinux-config --get-hw-description /data2/hw/nasrm/usb_wrapper.xsa

This will present a configuration screen. Don't forget to set the serial devices for boot messages and terminal access.

Then, configure the kernel with all of the necessary modules. Basically it's a good old linux menuconfig.

petalinux-config -c kernel

If the tinfo5 library is not found in ubuntu 24, you may symlink it somewhere or download from ubuntu 22:

sudo apt update

wget http://security.ubuntu.com/ubuntu/pool/universe/n/ncurses/libtinfo5_6.3-2ubuntu0.1_amd64.deb

sudo apt install ./libtinfo5_6.3-2ubuntu0.1_amd64.deb

NASR-M base controller works!

I’ve started populating the board, and the base controller worked. Although my long-term plan is to use a Zephyr, for simplicity, I resorted to a quick stub firmware written with STM32Cube that activates the ATX PSU and blinks the status LED. I’ve got the (primary) power!

The ever-growing “lessons learned” list has been updated with the following:

NASR-M clock generator preliminary config

The heart of the NASR-M carrier boards is the LMK03328 clock generator. It's an ultra-low noise and high-performance clock generator with two PLLs and eight outputs. The outputs can be set to single-ended or differential with an adjustable voltage level. The chip can switch between two reference inputs and is configured with I2C. In my case, the main reference input is the onboard TCXO, and the secondary is an external reference.

NASR-M first prototype production

Yesterday, I sent the initial NASR-M prototype for production to JLCPCB. Hoping there will be no obvious blockers and I'll be able to bootstrap Linux with no re-spins. I want to bring the board up circuit by circuit to know precisely what works and what doesn't.

NASR-M SYZYGY carrier board

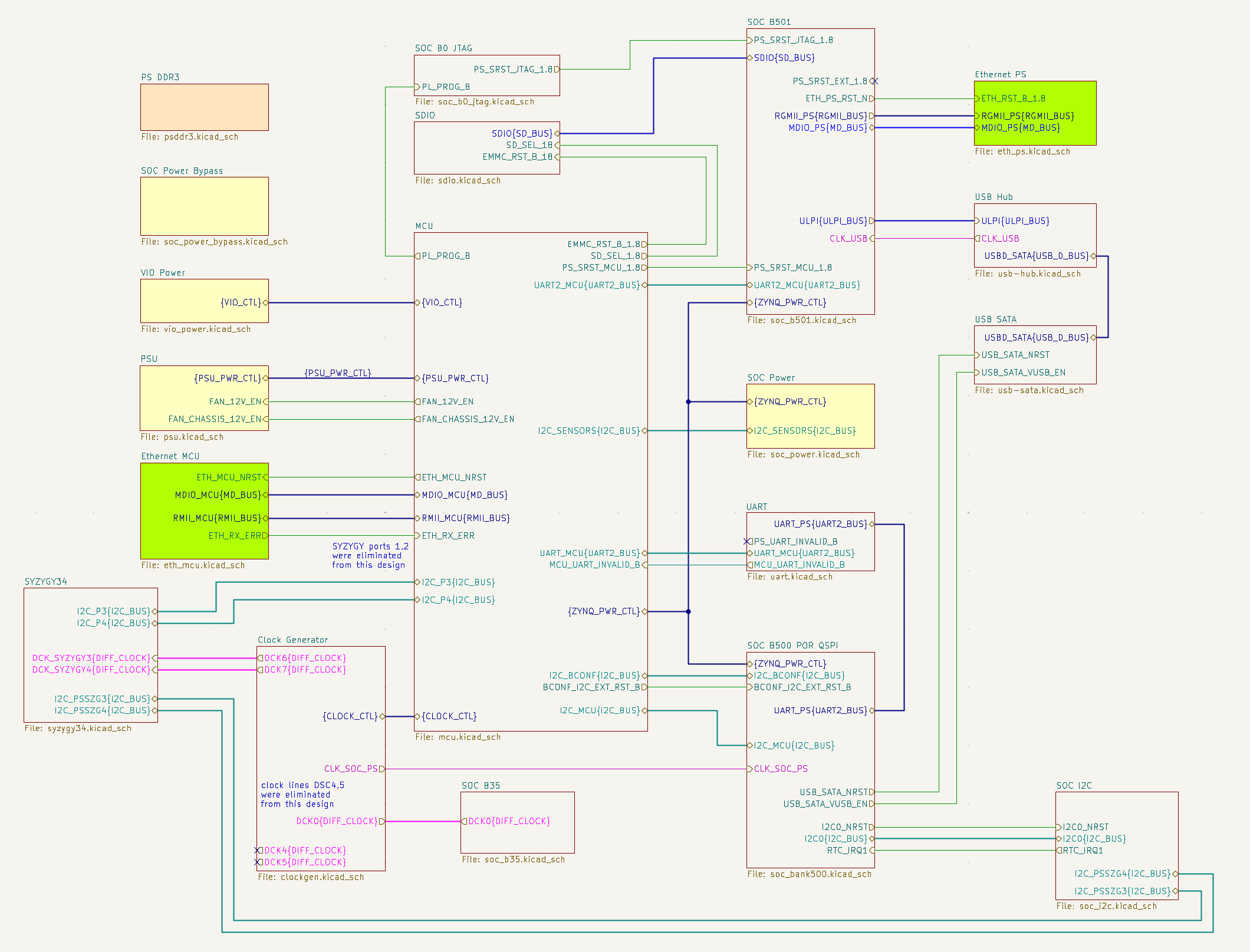

NASR-M

Some time ago, I decided to try Xilinx Zynq, which everyone is using in their RF projects. And what is a better option for exploring a new chip than making a board around it? Spending some money on a reference design devkit from the manufacturer? No, that's certainly not my way of learning things.

My dream board had 1GB of 32-bit-wide DDR3 RAM, SYZYGY ports, a standard ATX power supply, 1Gb ethernet port, and remote management that would allow me to flash firmware, control the system remotely, and export temperature and power usage readings to let me debug comfortably. Since that's my first rather complex embedded board in KiCad, I have made some dubious choices with PCB stackup, component placement, and routing. Sounds counterintuitive, but that was already a great learning experience in how not to do things and which design choices to avoid. It may work, however. I am pretty concerned about the DDR3 part, which was the most challenging part to route.

But if it works, I would have an excellent opportunity to play with software radio on a different level. And by different level, I mean a system built from scratch. Long story short, it's on a GitHub, completely open "with open-source everything". Once the board boots up, I will publish the Vivado design and the board MCU firmware sources. This will take some time, though. Once I'm more confident in design, I'll order PCBs from JLCPCB, and it will take even more time to solder the components in circuit by circuit, starting with the MCU, then the secondary PSU, and the rest. Scroll down into the long list of things that could break if you are interested in this rather dramatic development.

Design is made with KiCad 9. Below is a high-level overview of fundamental blocks.

lboard2 p. I - spartan-6 slave serial sonfiguration

The core of lboard2 is a Xilinx XC6SLX9 FPGA which was chosen because of the easy to solder TQG144 qfp package. Nowadays it's counted as a low density chip, but it's 9K LUT architecture is powerful enough for a simple audio processing. Spartan-6 hasn't got any non-volatile storage, so it has to be configured on every startup. Xilinx UG380 describes the various configuration options in details.

My configuration method of choice was Slave-Serial, because it was easy to implement with a suitable microcontroller. Basically it's a single data line serial protocol which transmits the configuration file bit by bit. Slave-Serial has several beneficial features: it requires only 5 signals, clock line is free running and the protocol is very easy.

lboard2 sound processing dev board with spartan-6 and aic3204

lboard2 is my take on building a simple DSP application using Xilinx Spartan-6 FPGA and TI TLV320AIC3204 audio codec from the scratch. I thought it's far more interesting to design my own booard instead of buying a commercially available development kit which just works. Currently, lboard2 is passing a loopback test, which means that audio samples are captured with a codec, being received on the FPGA pins, then routed back to a codec's DAC and heard with a headphones. Loopback isn't the most exciting application, so I'm working on a simple Fourier transfer based VU-meter. Once it's ready, I'll post the code, but before that, I'd like to share my experience with Spartan-6 in a series of a short posts tagged with an lboard2 label.

Hoping this information would help beginners to build a working system faster and with less pain.