lboard2 p. I - spartan-6 slave serial sonfiguration

The core of lboard2 is a Xilinx XC6SLX9 FPGA which was chosen because of the easy to solder TQG144 qfp package. Nowadays it's counted as a low density chip, but it's 9K LUT architecture is powerful enough for a simple audio processing. Spartan-6 hasn't got any non-volatile storage, so it has to be configured on every startup. Xilinx UG380 describes the various configuration options in details.

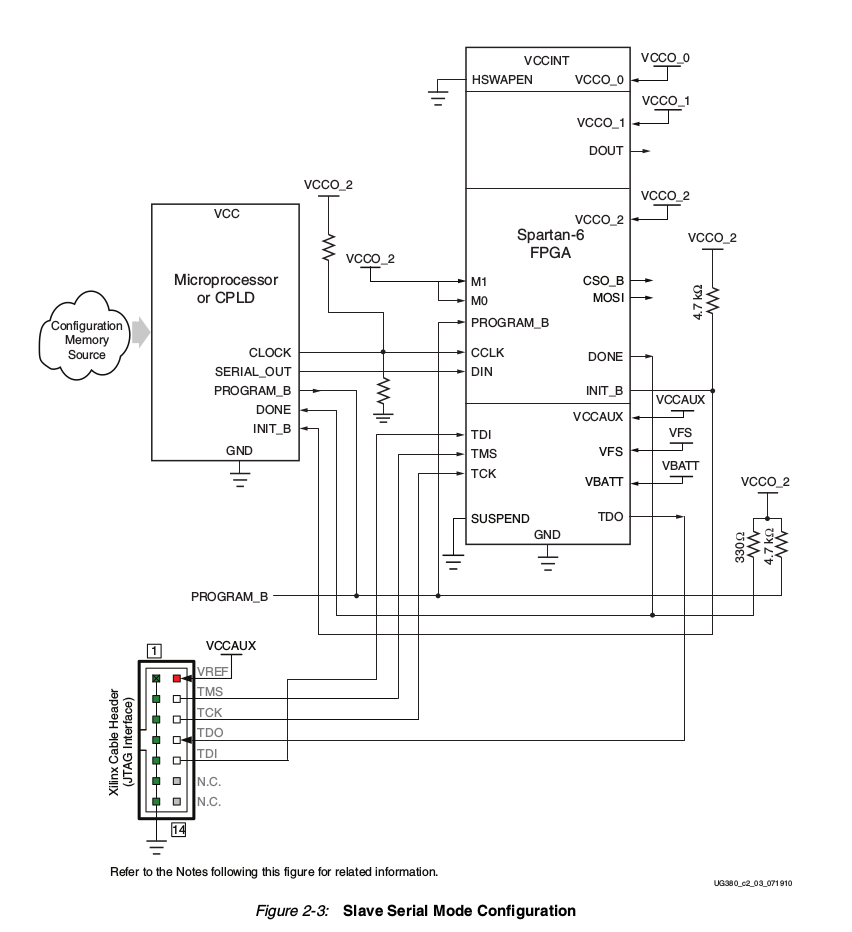

My configuration method of choice was Slave-Serial, because it was easy to implement with a suitable microcontroller. Basically it's a single data line serial protocol which transmits the configuration file bit by bit. Slave-Serial has several beneficial features: it requires only 5 signals, clock line is free running and the protocol is very easy.

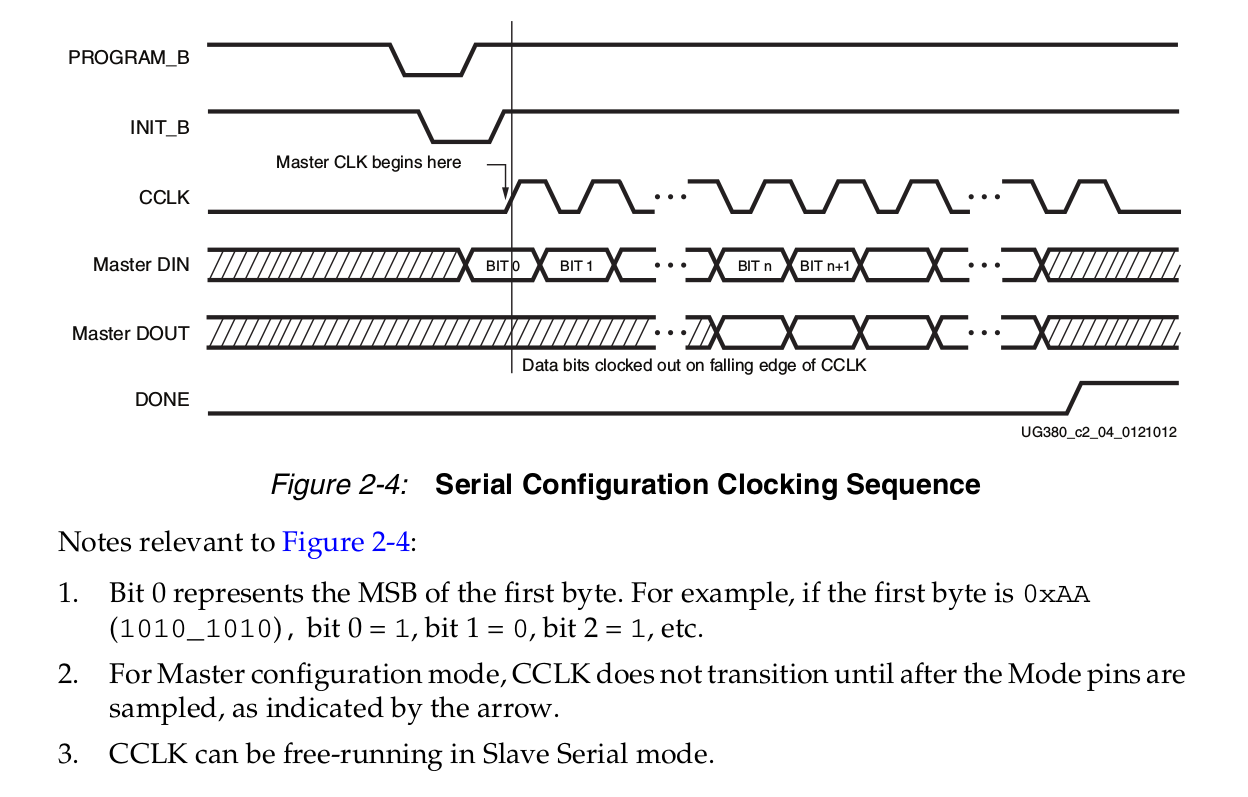

To start the configuration, set the PROGRAM_B high and wait until INIT_B is high, after that data is read on a rising CCLK front. Maximum configuration speed is around 30MHz for Spartan-6. Once the config file is completely transmitted, clock shall toggle for at least an 8 additional cycles. Signal DONE goes high when the configuration is complete.

To start the configuration, set the PROGRAM_B high and wait until INIT_B is high, after that data is read on a rising CCLK front. Maximum configuration speed is around 30MHz for Spartan-6. Once the config file is completely transmitted, clock shall toggle for at least an 8 additional cycles. Signal DONE goes high when the configuration is complete.

Configuration is controlled with an STM32F401RE MCU. STM32F401RE has a 512K of internal flash memory to store the FPGA config. Easiest and fastest to implement config upload was via a USB DFU protocol. Device Firmware Upgrade or DFU is a mechanism for 'downloading' firmware into device.

Configuration is controlled with an STM32F401RE MCU. STM32F401RE has a 512K of internal flash memory to store the FPGA config. Easiest and fastest to implement config upload was via a USB DFU protocol. Device Firmware Upgrade or DFU is a mechanism for 'downloading' firmware into device.

Since I'm a GNU / Linux user, I'm using a dfu-util by Stefan Schmidt & Tormod Volden. There should be other utilities for different operating systems which do the same thing.

My bootloader is written using a popular STM32Cube software, it's called lboard2flashboot. README has a better description of what it does and how to use it.

There are few things I'd like to note about the Slave-Serial configuration. Line CCLK is terminated with a two 100 Ohm resistors to prevent ringing, don't forget to do that.

The second thing which nearly drew me crazy was a positive pull-up on a CSI_B pin. Xilinx recommends to pull-up the unused pins or leave them hanging. I was overzealous and pulled the CSI_B high, however FPGA was not "booting" until I cut open the CSI_B trace with an exacto knife. Don't pull CSI_B high when using a Slave-Serial, stay lazy and leave it unconnected.