NASR-M clock generator preliminary config

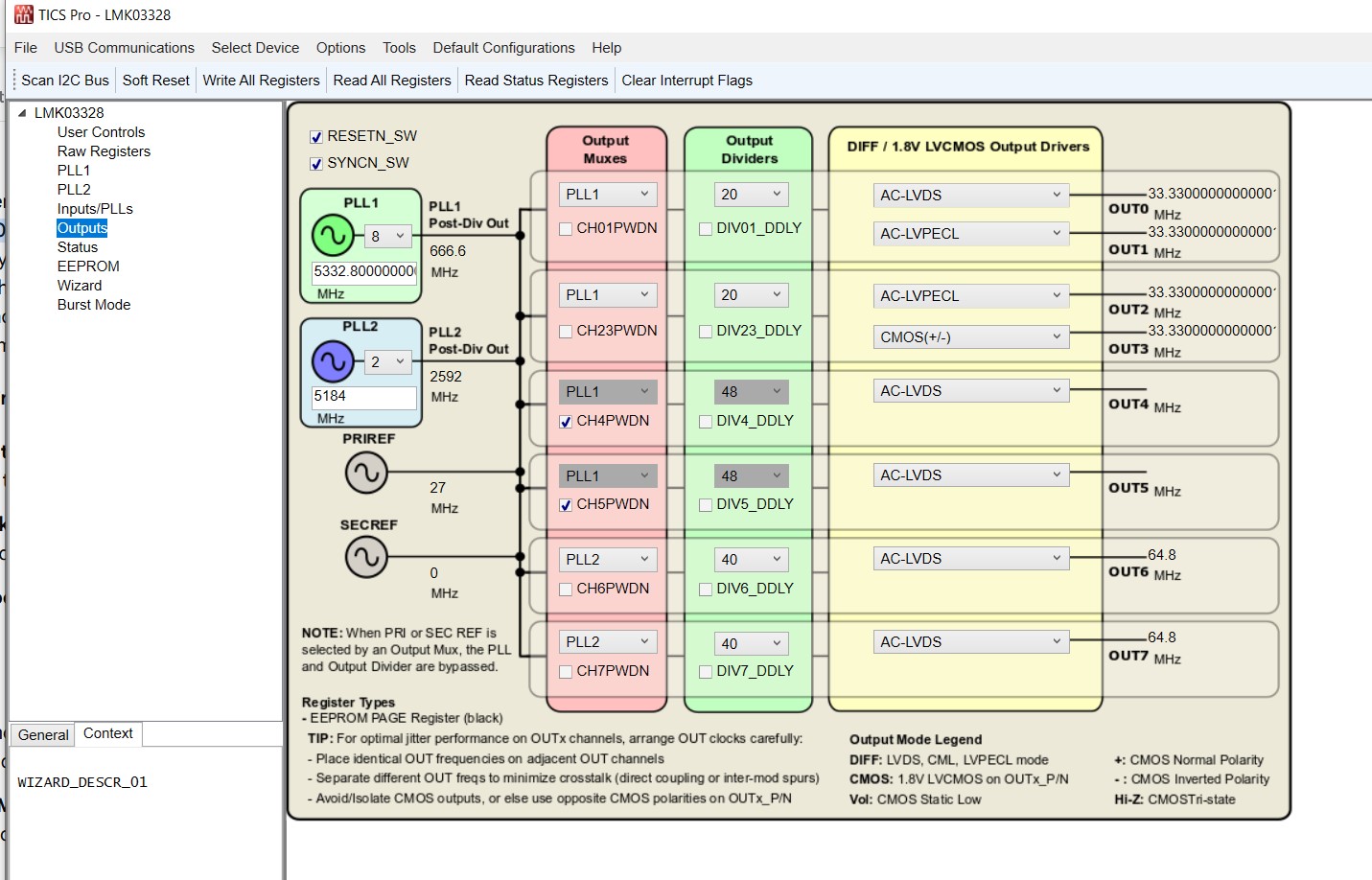

The heart of the NASR-M carrier boards is the LMK03328 clock generator. It's an ultra-low noise and high-performance clock generator with two PLLs and eight outputs. The outputs can be set to single-ended or differential with an adjustable voltage level. The chip can switch between two reference inputs and is configured with I2C. In my case, the main reference input is the onboard TCXO, and the secondary is an external reference.

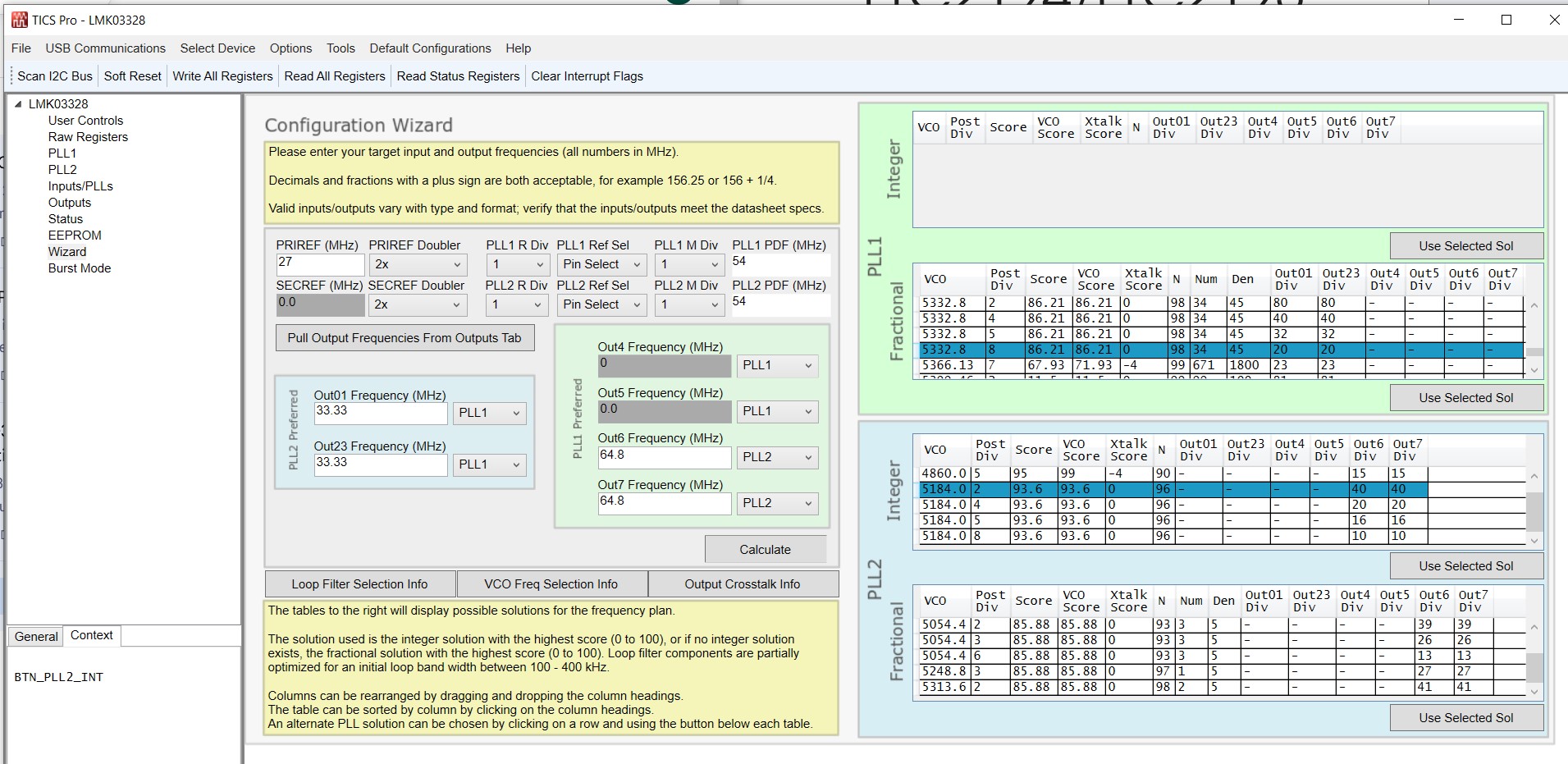

Configuring the right registers for fractional frequencies and avoiding crosstalk between the PLLs is not as easy as it seems. Luckily, TI provides a TICS Pro software, which includes a GUI solver that does all the magic. All you need to do is choose the right device (LMK03328) and enter the required frequencies per output. If the program detects spurious output or crosstalk, it displays a warning message dialog. Sweet!

I want 33.33 MHz for the SOC PS and double 64.8 MHz for the SYZYGY ports. Why fractional? For the SOC PS, it’s a recommended frequency that feeds its PLL. The 64.8 for the SYZYGY carrier-to-pod clock was chosen to avoid spurs.

Once you’ve got the right configuration, you can save the solution for later use and export the register map into a text file. Let’s see how this works.