NASR-M board bring-up, first Linux boot

Today I was happily observing Linux boot messages on a NASR-M tty console. It was a major milestone in development. I decided to generate the PetaLinux image using the traditional workflow and leave the Yocto exploration for later. Sadly, good old PetaLinux tools will be deprecated in favor of Yocto in 2026.

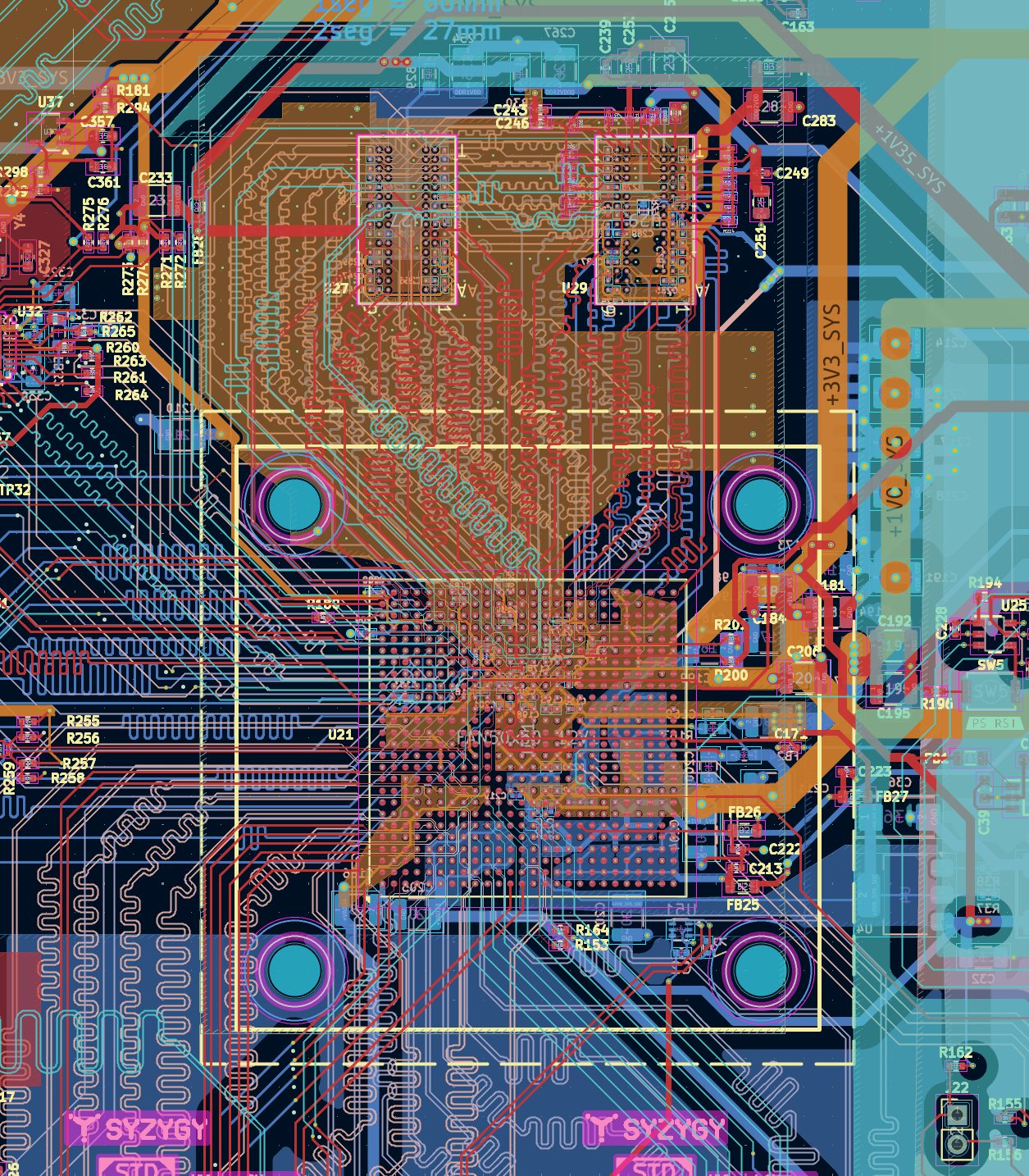

NASR-M board bring-up, DDR3 test

Today is an important milestone in a board bring-up, as the DDR3 subsystem appears functional. I was able to run a Vivado bundled Zynq bare-metal DDR test with no errors. The test image was uploaded via JTAG and executed on a CPU core.

That was the most important indication of a system's health to me. Even if other subsystems don’t work properly, I’ll be able to respin the board with minimal effort. There are a few things to improve. Most importantly, the data strobe line length. Currently, the propagation delay between the strobe and data lines is very short, less than 0.01 nanoseconds. I suppose that contributed to somewhat narrow write eye width.

But hey, 65-71% is still ok, and definitely acceptable for a first prototype. Even without post-routing simulations, I’ve got a nice result. This routing won’t win the beauty contest, but at least it works, and someone may find it useful. Learn from my mistakes, kids :)

I’ve seen a lot of requests on the forums regarding fly-by topology applied to Zynq 7000, so here are a few tips and rules of thumb that worked for me: